## **Towards Designing PCM-Conscious Database Systems**

A THESIS SUBMITTED FOR THE DEGREE OF **Master of Science (Engineering)** IN THE Faculty of Engineering

> BY Vishesh Garg

Department of Computational and Data Sciences Indian Institute of Science Bangalore – 560 012 (INDIA)

March 2016

DEDICATED TO

My Beloved Master

Shri Parthasarathi Rajagopalachari

# Acknowledgements

No thesis acknowledgment can begin without thanking one's advisor – not out of compulsion but out of gratitude for the things that one gets to learn from him/her. In my case it's no different, as I consider working under Prof. Jayant Haritsa a turning point in my life. If it was not for him, I would perhaps have never known what research is all about, what should our attitude be towards work, and how we should keep striving for perfection in everything that we do.

Next, I would like to thank my lab members – Anshuman, Srinivas and Rafia among several others – who provided critical feedback for my work and acted as support in trying times during my stay here.

Finally, I would like to thank my family who encouraged me to pursue higher studies even after spending a considerable time working in the industry.

## Abstract

Phase Change Memory (PCM) is a recently developed non-volatile memory technology that is expected to provide an attractive combination of the best features of conventional disks (persistence, capacity) and of DRAM (access speed). For instance, it is about 2 to 4 times denser than DRAM, while providing a DRAM-comparable read latency. On the other hand, it consumes much less energy than magnetic hard disks while providing substantively smaller write latency. Due to this suite of desirable features, PCM technology is expected to play a prominent role in the next generation of computing systems, either augmenting or replacing current components in the memory hierarchy. A limitation of PCM, however, is that there is a significant difference between the read and write behaviors in terms of energy, latency and bandwidth. A PCM write, for example, consumes 6 times more energy than a read. Further, PCM has limited write endurance since a memory cell becomes unusable after the number of writes to the cell exceeds a threshold determined by the underlying glass material.

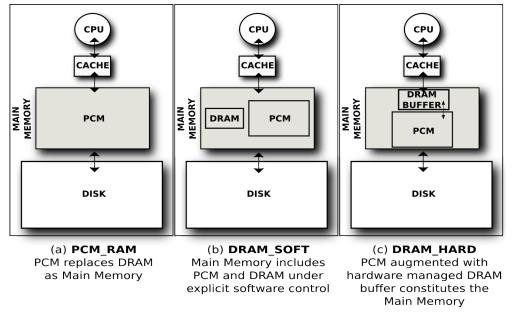

Database systems, by virtue of dealing with enormous amounts of data, are expected to be a prime beneficiary of this new technology. Accordingly, recent research has investigated how database engines may be redesigned to suit DBMS deployments on PCM, covering areas such as indexing techniques, logging mechanisms and query processing algorithms. Prior database research has primarily focused on computing architectures wherein either a) PCM completely replaces the DRAM memory ; or b) PCM and DRAM co-exist side-by-side and are independently controlled by the software. However, a third option that is gaining favor in the architecture community is where the PCM is augmented with a small hardware-managed DRAM buffer. In this model, which we refer to as **DRAM\_HARD**, the address space of the application maps to PCM, and the DRAM buffer can simply be visualized as yet another level of the existing cache hierarchy. With most of the query processing research being preoccupied with the first two models, this third model has remained largely ignored. Moreover, even in this limited literature, the emphasis has been restricted to exploring execution-time strategies; the compile-time plan selection process itself being left unaltered.

In this thesis, we propose minimalist reworkings of current implementations of database operators, that are tuned to the DRAM\_HARD model, to make them PCM-conscious. We also propose novel algorithms for compile-time query plan selection, thereby taking a holistic approach to introducing PCM-compliance in present-day database systems. Specifically, our contributions are two-fold, as outlined below.

First, we address the pragmatic goal of minimally altering current implementations of database operators to make them PCM-conscious, the objective being to facilitate an easy transition to the new technology. Specifically, we target the implementations of the "workhorse" database operators: sort, hash join and group-by. Our customized algorithms and techniques for each of these operators are designed to significantly reduce the number of writes while simultaneously saving on execution times. For instance, in the case of sort operator, we perform an in-place partitioning of input data into DRAM-sized chunks so that the subsequent sorting of these chunks can finish inside the DRAM, consequently avoiding both intermediate writes and their associated latency overheads.

Second, we redesign the query optimizer to suit the new environment of PCM. Each of the new operator implementations is accompanied by simple but effective write estimators that make these implementations suitable for incorporation in the optimizer. Current optimizers typically choose plans using a latency-based costing mechanism assigning equal costs to both read and write memory operations. The asymmetric read-write nature of PCM implies that these models are no longer accurate. We therefore revise the cost models to make them cognizant of this asymmetry by accounting for the additional latency during writes. Moreover, since the number of writes is critical to the lifespan of a PCM device, a new metric of write cost is introduced in the optimizer plan selection process, with its value being determined using the above estimators.

Consequently, the query optimizer needs to select plans that simultaneously minimize query writes and response times. We propose two solutions for handling this dual-objective optimization problem. The first approach is a heuristic propagation algorithm that extends the widely used dynamic programming plan propagation procedure to drastically reduce the exponential search space of candidate plans. The algorithm uses the write costs of sub-plans at each of the operator nodes to decide which of them can be selectively pruned from further consideration. The second approach maps this optimization problem to the linear multiple-choice knapsack problem, and uses its greedy solution to return the final plan for execution. This plan is known to be optimal within the set of non interesting-order plans in a single join order search space. Moreover, it may contain a weighted execution of two algorithms for one of the operator nodes in the plan tree. Therefore overall, while the greedy algorithm comes with optimality guarantees, the heuristic approach is advantageous in terms of easier implementation.

The experimentation for our proposed techniques is conducted on Multi2sim, a state-ofthe-art cycle-accurate simulator. Since it does not have native support for PCM, we made a major extension to its existing memory module to model PCM device. Specifically, we added separate data tracking functionality for the DRAM and PCM resident data, to implement the commonly used read-before-write technique for PCM writes reduction. Similarly, modifications were made to Multi2sim's timing subsystem to account for the asymmetric read-write latencies of PCM. A new DRAM replacement policy called N-Chance, that has been shown to work well for PCM-based hardware, was also introduced.

Our new techniques are evaluated on end-to-end TPC-H benchmark queries with regard to the following metrics: number of writes, response times and wear distribution. The experimental results indicate that, in comparison to their PCM-oblivious counterparts, the PCM-conscious operators collectively reduce the number of writes by a factor of 2 to 3, while concurrently improving the query response times by about 20% to 30%. When combined with the appropriate plan choices, the improvements are even higher. In the case of Query 19, for instance, we obtained a 64% savings in writes, while the response time came down to two-thirds of the original. In essence, our algorithms provide both short-term and long-term benefits. These outcomes augur well for database engines that wish to leverage the impending transition to PCM-based computing.

# Publications based on this Thesis

- Vishesh Garg, Abhimanyu Singh, Jayant R. Haritsa, *"Towards Making Database Systems PCM-Compliant"*, Proc. of 26th Intl. Conf. on Database and Expert Systems Applications (DEXA), Valencia, Spain, September 2015 (to appear)

- Vishesh Garg, Abhimanyu Singh, Jayant R. Haritsa,

"On Improving Write Performance in PCM Databases", Technical Report, TR-2015-01,

DSL/SERC, Indian Institute of Science

http://dsl.serc.iisc.ernet.in/publications/report/TR/TR-2015-01.pdf

# Contents

| A              | cknov | wledgements                     | i  |

|----------------|-------|---------------------------------|----|

| A              | bstra | ct                              | ii |

| $\mathbf{P}_1$ | ublic | ations based on this Thesis     | i  |

| C              | onter | vi                              | ii |

| Li             | st of | Figures                         | i  |

| Li             | st of | Tables                          | ii |

| K              | eywo  | rds                             | V  |

| 1              | Intr  | oduction                        | 1  |

|                | 1.1   | Phase Change Memory             | 3  |

|                | 1.2   | Architectural Model             | 5  |

|                | 1.3   | Problem Framework               | 6  |

|                | 1.4   | Organization                    | 8  |

| <b>2</b>       | Sur   | vey of Related Literature       | 9  |

|                | 2.1   | Architectural techniques        | 9  |

|                | 2.2   | Programming models and APIs 1   | 2  |

|                | 2.3   | Application-level optimizations | 4  |

|   | 2.4 | Optim        | nizations for flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 |

|---|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3 | Ope | erator       | Execution Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |

|   | 3.1 | The $S$      | ort Operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

|   |     | 3.1.1        | Data with uniform distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21 |

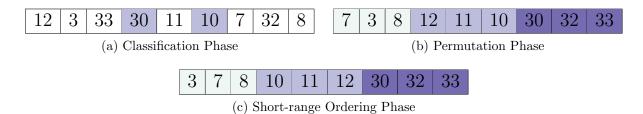

|   |     |              | 3.1.1.1 Classification phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22 |

|   |     |              | 3.1.1.2 Permutation phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 |

|   |     |              | 3.1.1.3 Short-range Ordering phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22 |

|   |     | 3.1.2        | Data with non-uniform distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22 |

|   |     |              | 3.1.2.1 Classification phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

|   |     |              | 3.1.2.2 Permutation phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|   |     |              | 3.1.2.3 Short-range Ordering phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |

|   |     | 3.1.3        | PCM write analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25 |

|   |     | 3.1.4        | Response time analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 |

|   | 3.2 | The <i>H</i> | Iash Join Operator   Image: Constraint of the second sec | 29 |

|   |     | 3.2.1        | PCM write analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

|   |     | 3.2.2        | Response time analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

|   | 3.3 | The G        | Group-By Operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

|   |     | 3.3.1        | Hash-Based Grouping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

|   |     |              | 3.3.1.1 PCM write analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 |

|   |     |              | 3.3.1.2 Response time analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

|   |     | 3.3.2        | Sort-Based Grouping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34 |

|   |     |              | 3.3.2.1 PCM write analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

|   |     |              | 3.3.2.2 Response time analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35 |

| 4 | Imp | olemen       | tation Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

|   | 4.1 |              | tors Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

|   |     | 4.1.1        | Sort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

|   |     |              | 4.1.1.1 Uniform Data Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

|   |                                                           |                                                                                           | 4.1.1.2 Non-Uniform Data Distribution | 38                                                 |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------|

|   |                                                           | 4.1.2                                                                                     | Hash Join                             | 39                                                 |

|   |                                                           | 4.1.3                                                                                     | Group-By                              | 39                                                 |

|   |                                                           |                                                                                           | 4.1.3.1 Sort-based Grouping           | 40                                                 |

|   |                                                           |                                                                                           | 4.1.3.2 Hash-based Grouping           | 40                                                 |

|   | 4.2                                                       | Simula                                                                                    | ator Enhancements                     | 40                                                 |

|   |                                                           | 4.2.1                                                                                     | Hybrid Main Memory                    | 41                                                 |

|   |                                                           | 4.2.2                                                                                     | New DRAM Replacement Policy           | 41                                                 |

|   |                                                           | 4.2.3                                                                                     | Tracking DRAM-PCM Data                | 41                                                 |

|   |                                                           | 4.2.4                                                                                     | Data Comparison Write Scheme          | 42                                                 |

|   |                                                           | 4.2.5                                                                                     | Asymmetric Read-Write Latencies       | 42                                                 |

|   |                                                           | 4.2.6                                                                                     | Wear Distribution                     | 43                                                 |

|   |                                                           | 4.2.7                                                                                     | Intermediate Statistics               | 43                                                 |

| 5 | Evn                                                       | orimo                                                                                     | ntal Evaluation                       | 44                                                 |

| 0 | пур                                                       |                                                                                           |                                       |                                                    |

|   | ۲ 1                                                       | A . 1 · 4                                                                                 |                                       |                                                    |

|   | 5.1                                                       |                                                                                           | cectural Platform                     |                                                    |

|   | $5.1 \\ 5.2$                                              |                                                                                           | ectural Platform                      | 44<br>45                                           |

|   |                                                           |                                                                                           |                                       |                                                    |

|   |                                                           | Datab                                                                                     | ase and Queries                       | 45                                                 |

|   |                                                           | Datab<br>5.2.1<br>5.2.2                                                                   | ase and Queries                       | 45<br>46                                           |

|   | 5.2                                                       | Datab<br>5.2.1<br>5.2.2<br>Perfor                                                         | ase and Queries                       | 45<br>46<br>47<br>48                               |

|   | 5.2<br>5.3                                                | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper                                                | pase and Queries                      | 45<br>46<br>47<br>48                               |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>             | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper                                                | ase and Queries                       | 45<br>46<br>47<br>48<br>49                         |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>             | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper                                                | ase and Queries                       | 45<br>46<br>47<br>48<br>49<br>51                   |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>             | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper<br>Opera<br>5.5.1                              | ase and Queries                       | 45<br>46<br>47<br>48<br>49<br>51<br>51             |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>             | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper<br>Opera<br>5.5.1<br>5.5.2<br>5.5.3            | ase and Queries                       | 45<br>46<br>47<br>48<br>49<br>51<br>51<br>51       |

|   | <ul><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul> | Datab<br>5.2.1<br>5.2.2<br>Perfor<br>Exper<br>Opera<br>5.5.1<br>5.5.2<br>5.5.3<br>Lifetin | ase and Queries                       | 45<br>46<br>47<br>48<br>49<br>51<br>51<br>51<br>52 |

|    |                | 5.8.1   | Sort                                   | 55 |  |

|----|----------------|---------|----------------------------------------|----|--|

|    |                | 5.8.2   | Hash Join                              | 56 |  |

|    |                | 5.8.3   | Group-By                               | 58 |  |

| 6  | Que            | ery Op  | timizer Integration                    | 59 |  |

|    | 6.1            | Heuris  | tic-Propagation Algorithm              | 60 |  |

|    |                | 6.1.1   | Experimental Results                   | 63 |  |

|    | 6.2            | Greed   | y Algorithm                            | 65 |  |

|    | 6.3            | Illustr | ative example comparing the algorithms | 69 |  |

|    |                | 6.3.1   | Heuristic-Propagation Algorithm        | 71 |  |

|    |                | 6.3.2   | Greedy Algorithm                       | 72 |  |

| 7  | Cor            | nclusio | n                                      | 78 |  |

| Bi | ibliography 81 |         |                                        |    |  |

# List of Figures

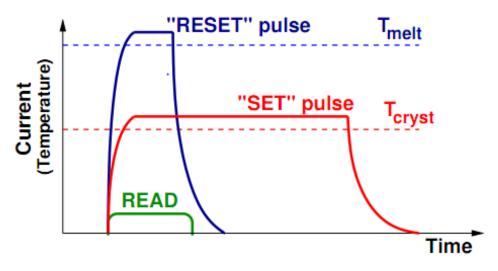

| 1.1  | Programming the PCM cell [12]                       | 4  |

|------|-----------------------------------------------------|----|

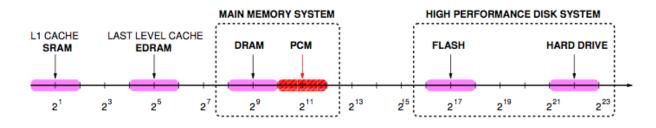

| 1.2  | Typical access cycles for different memories $[32]$ | 4  |

| 1.3  | PCM-based Architectural Options [12]                | 6  |

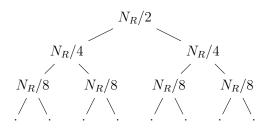

| 3.1  | Multi-Pivot Flashsort                               | 26 |

| 3.2  | Recursion tree for quicksort swaps                  | 26 |

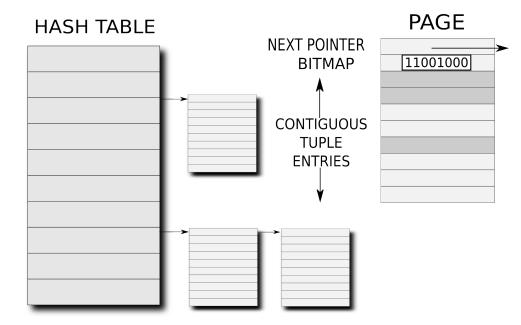

| 3.3  | Paged Hash Table                                    | 31 |

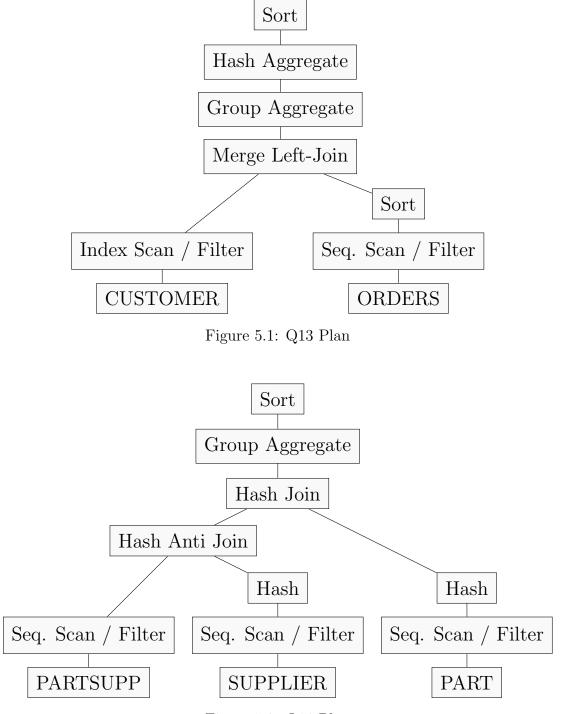

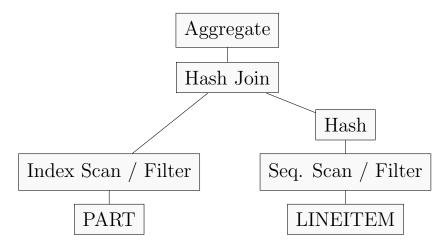

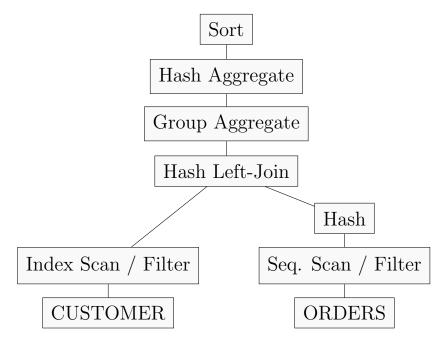

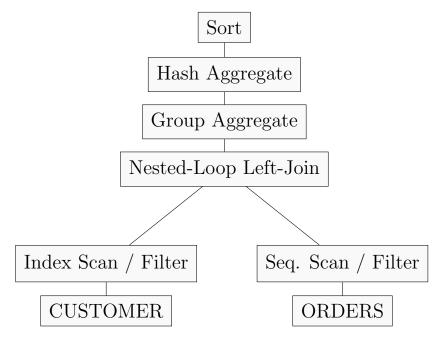

| 5.1  | Q13 Plan                                            | 47 |

| 5.2  | Q16 Plan                                            | 48 |

| 5.3  | Q19 Plan                                            | 48 |

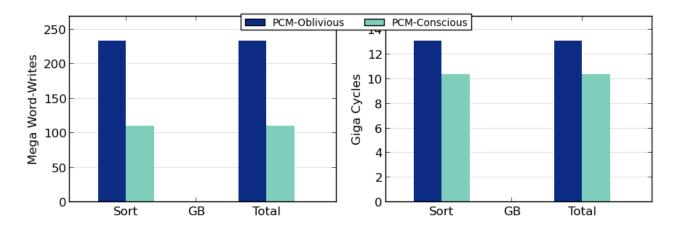

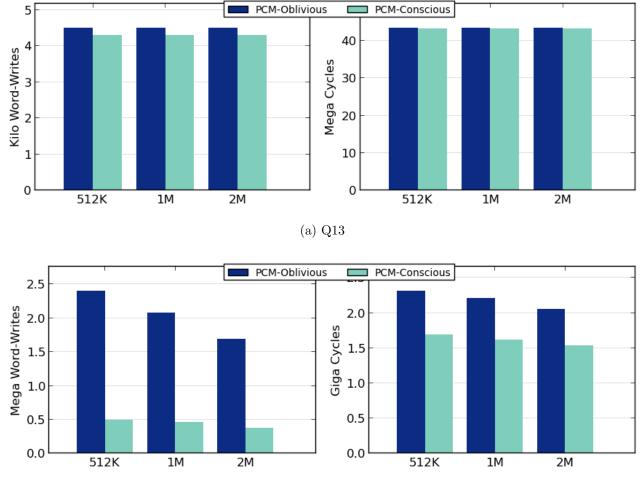

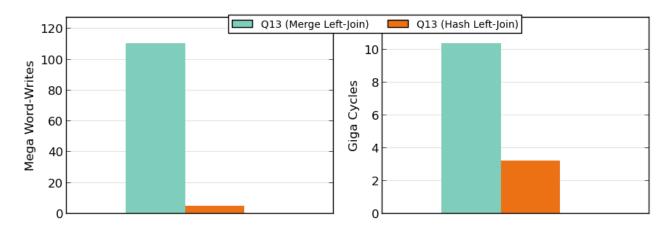

| 5.4  | Q13 Performance                                     | 49 |

| 5.5  | Q13 Performance (skewed TPC-H)                      | 50 |

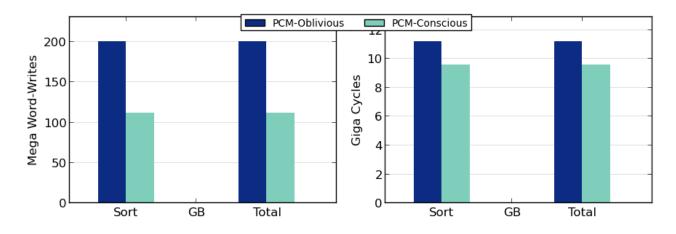

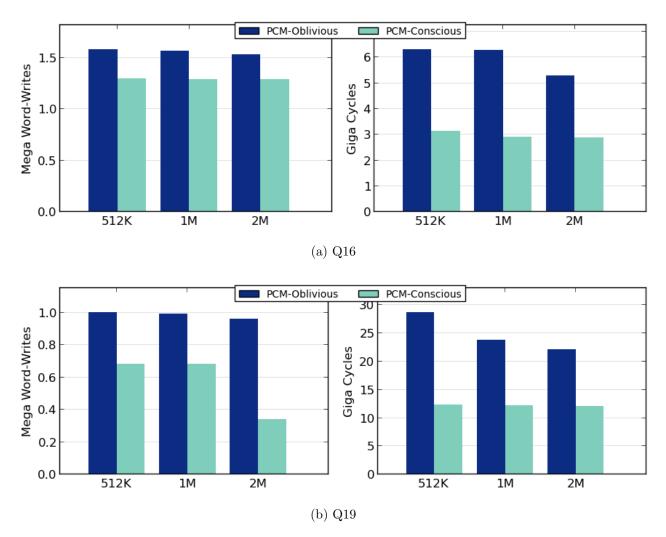

| 5.6  | Q16 Performance                                     | 50 |

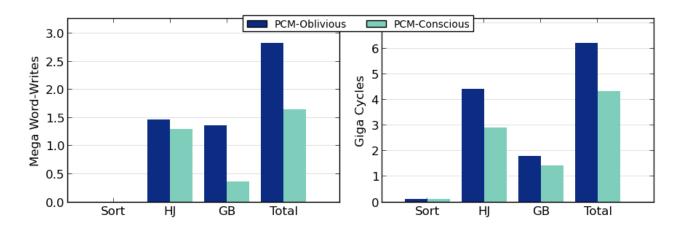

| 5.7  | Q19 Performance                                     | 51 |

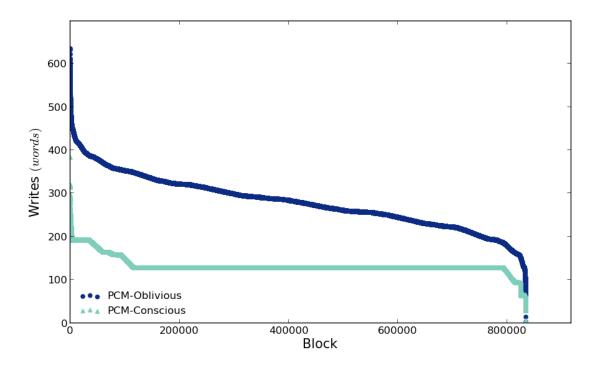

| 5.8  | Q13 wear distribution                               | 53 |

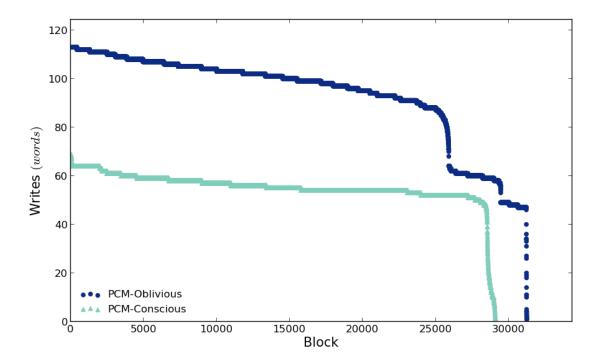

| 5.9  | Q16 wear distribution                               | 53 |

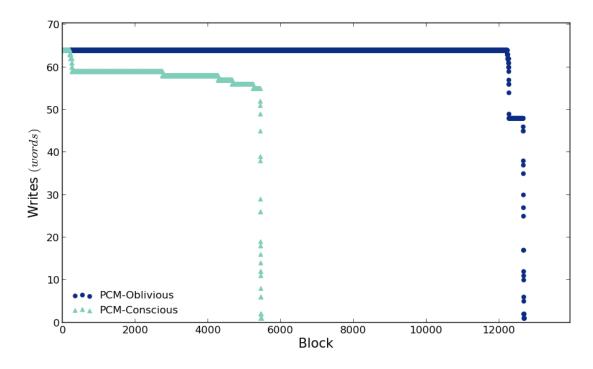

| 5.10 | Q19 wear distribution                               | 54 |

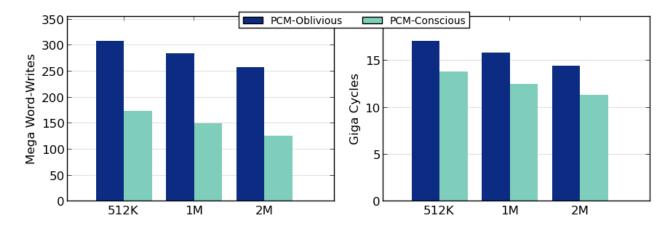

| 5.11 | Sort (Q13)                                          | 55 |

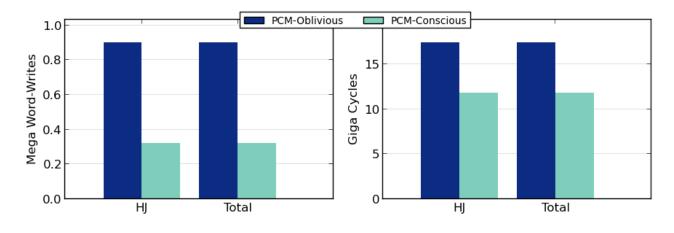

| 5.12 | Hash Join                                           | 56 |

| 5.13 | Group By                                            | 57 |

| 6.1  | Q13 Plan with revised latency costs                       | 61 |

|------|-----------------------------------------------------------|----|

| 6.2  | Q13 Plan with slack ( $\lambda$ ) value of 5              | 62 |

| 6.3  | Integration with Query Optimization and Processing Engine | 62 |

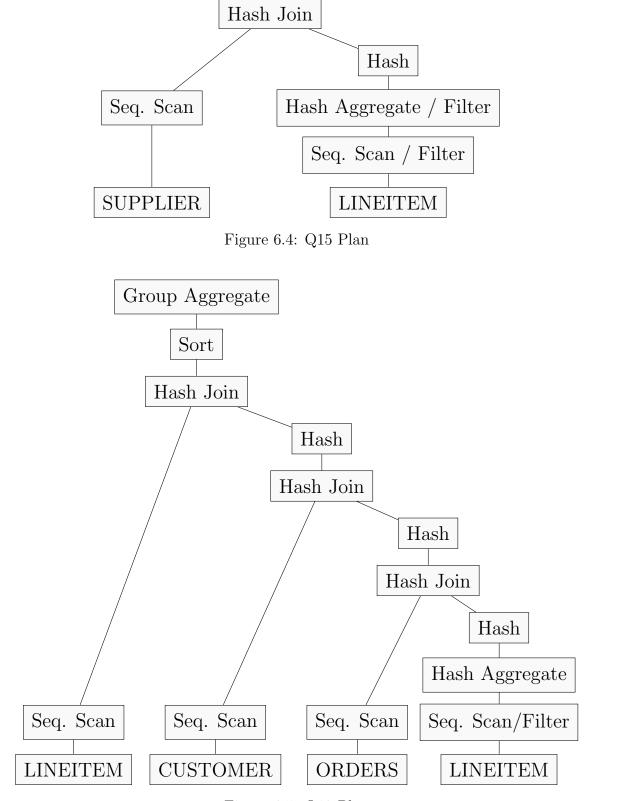

| 6.4  | Q15 Plan                                                  | 64 |

| 6.5  | Q18 Plan                                                  | 64 |

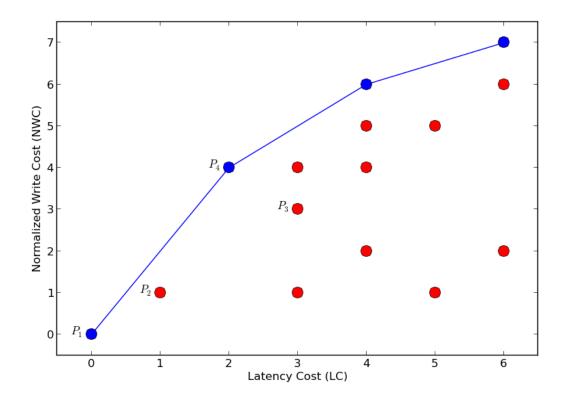

| 6.6  | LP-undominated algorithms (blue)                          | 69 |

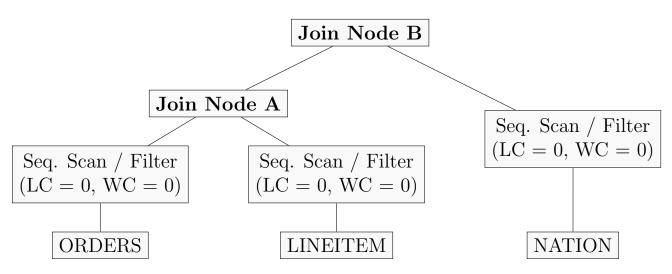

| 6.7  | Query Plan Tree Structure                                 | 70 |

| 6.8  | LC-optimal plan $(P_1)$                                   | 70 |

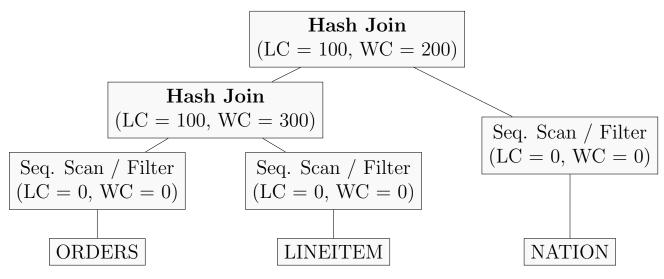

| 6.9  | Enumeration Algorithm plan $(P_5)$                        | 72 |

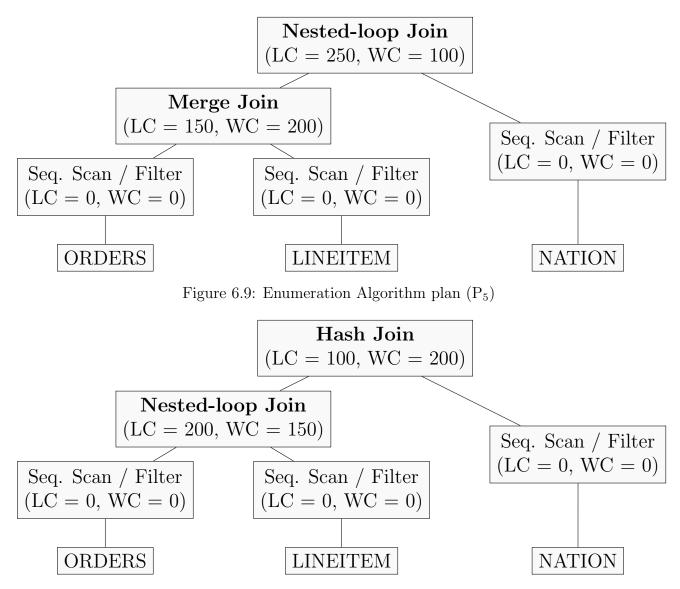

| 6.10 | Heuristic-Propagation Algorithm plan $(\mathrm{P}_3)$     | 72 |

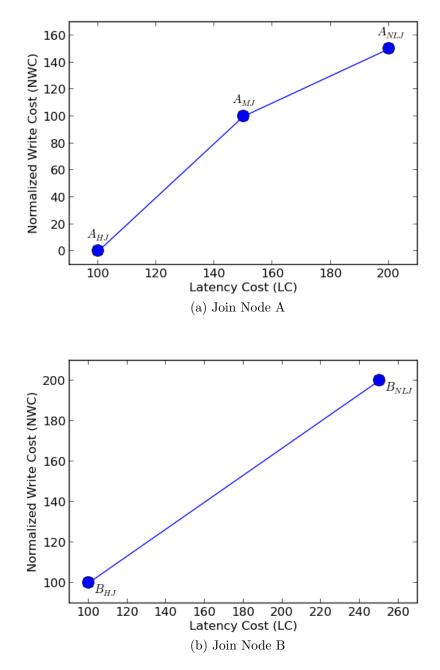

| 6.11 | Plot of algorithm costs                                   | 74 |

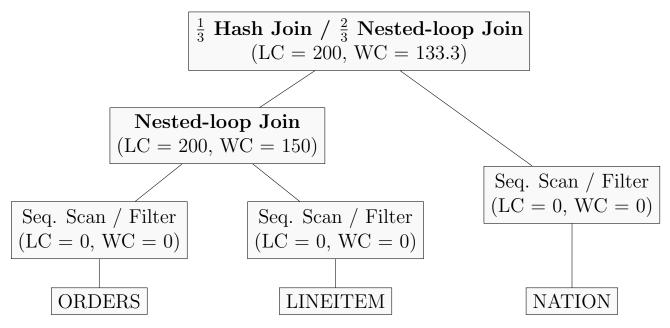

| 6.12 | Greedy Algorithm Plan                                     | 76 |

# List of Tables

| 1.1 | Comparison of memory technologies $[32]$ , $[25]$ , $[3]$ , $[12]$   | 5  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Notations Used in Operator Analysis                                  | 7  |

| 5.1 | Experimental Setup                                                   | 45 |

| 5.2 | Validation of Write Estimators                                       | 58 |

| 6.1 | Comparison of plans generated by Heuristic Algorithm $(\lambda = 1)$ | 63 |

# Keywords

Phase Change Memory, PCM, Database Operators, Sort, Hash Join, Group-By, Query Optimizer, Query Executor, Multi-Objective Query Optimization

## Chapter 1

# Introduction

Phase Change Memory (PCM) is a recently developed non-volatile memory technology, constructed from chalcogenide glass material, that stores data by switching between amorphous (*binary*  $\theta$ ) and crystalline (*binary* 1) states. Broadly speaking, it is expected to provide an attractive combination of the best features of conventional disks (persistence, capacity) and of DRAM (access speed). For instance, it is about 2 to 4 times denser than DRAM, while providing a DRAM-comparable read latency. On the other hand, it consumes much less energy than magnetic hard disks while providing substantively smaller write latency. Due to this suite of desirable features, PCM technology is expected to play a prominent role in the next generation of computing systems, either augmenting or replacing current components in the memory hierarchy [32, 46, 25]. A limitation of PCM, however, is that there is a significant difference between the read and write behaviors in terms of energy, latency and bandwidth. A PCM write, for example, consumes 6 times more energy than a read. Further, PCM has limited write endurance since a memory cell becomes unusable after the number of writes to the cell exceeds a threshold determined by the underlying glass material.

In the recent years, chip manufacturers have come up with new PCM prototypes and products signalling the advent of PCM-based systems. IBM, for example, has come up with a PCM prototype that is about 275 times faster than regular solid state disk (SSD) devices [6]. Companies like Micron [5] have made PCM chips available to original equipment manufacturers (OEM) to be included in their products. Similarly, Samsung has started shipping a PCMinclusive multi-chip package (MCP) that is intended for the mobile handset market [4]. These developments indicate that the transition of present computing systems to a PCM inclusive hardware is indeed imminent. Thus, it is imperative for database systems to be geared up for this transition if they are to utilize PCM to the fullest potential.